Fft For Risc For Mac

This paper is about the reduced instruction set computer (RISC), microprocessor CPU design that flavors a smaller and simpler set of instruction. In this project we have described 16-bit pipelined RISC processor for applications such as in real time digital signal processor and embedded systems. The processor designed specifically for DSP systems such as FFT, DWT, Convolution and ALU, executes most of instructions in a single cycle; conventional processors usually performs only arithmetic and mathematical operations.

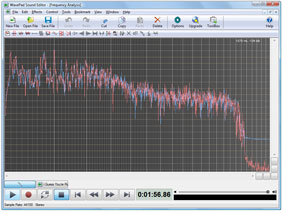

Hence RISC processors have complex control system which requires more clock cycle to operate, thus we overcome this problem using pipelined architecture of 4 stages i.e fetch, decode, execute and write back. In fact compared to base paper the area is reduced and speed is increased. The Simulation is done on XILINX 14.5i tool, implemented on SPARTAN-6 kit. Over all speed is achieved and results are verified. Patterson of berkeley RISC project. It is CPU design based on a simplified instruction set which provides higher performance when combined with microprocessor architecture which can handle executing those instructions using fewer cycles per instruction. The general concept is that the system uses small, highly optimized set of instruction instead of more variable set of instructions frequently found in other types of architecture.

The famous RISC families include AMD, Atmel2900, MIPS, SPARC and RISCV. Complex instruction set computer (CISC) opposed trend to RISC. Where as in RISC it uses load and store instructions refer data in memory, it uses fewer addressing modes with fixed length of instruction and unique format. Main characteristics of RISC microprocessor is it needs hard-wired, instead of using micro programming and also to implement CPU takes less area, speed are increased.

As known RISC was used to perform ALU operations generally, so to use for custom design i.e for different DSP applications this can be achieved using RISC Processor. In this project we are using pipelined architecture. In present era the development of CMOS technology yields very high density and high performance integrated circuits. This estimates that as increasing devices on chip which as well increases the overall performance of device but it has disadvantage of power consumption also becomes serious terrifying issue along with complexity of circuits. Hence, it becomes inevitable to implement less complex, low power processors.

In this work combination of RISC and DSP is done to improve speed of processor.

RISC and CISC have taken on new meanings in recent years. RISC used to mean Reduced Instruction Set Computing, but lately, RISC processors have nearly as many instructions as the CISC processors used to have. More so now, it means that the majority of available instructions can be performed in one or two clock cycles, rather than the 5 or 6 of traditional CISC. The PowerPC line fits into this description quite well. With AltiVec, it handles many instructions. CISC processors still have many instructions, but more of them require less time to process. The processors have taken on other RISC characteristics as well.

In fact, the Athlon processors from AMD have always been RISC processors emulating CISC x86 processors. Like bousozouku said, there has been a lot of conversion between the two as they relate to PPC and x86 processors recently. At this point, though PPCs are 'more RISCy' and Intel's chips (the P4/Xeon series, anyway) are 'more CISCy', it's not exactly accurate to put either label on either line of processors. You could probably say that things have probably gone toward a RISC-style core with higher-level CISC-style instruction set (or instructions that make use of seperate computation engines on the same chip, ala AltiVec), which seems to be the most efficient way of going about things. So far as I know, the same is pretty much true of most modern high-end procecssors; they all use some of both worlds, so it's more of a continuum than any sort of hard division. Not that you couldn't still have a 'real' RISC or CISC chip, just most aren't (and of course even those divisions aren't defined in terms of hard numbers, they're just design philosophies). For an example of a 'real' RISC chip, look at the now dead and much mourned Alpha chip series (made by DEC, then Compaq).

Fft For Risc For Macular Degeneration

For a real CISC chip (afaik) try an Intel 80286 or a Motorola 68xxx. Current chips are (as said above) really hybrids, with x86 chips breaking down instructions to be more RISC like, and PowerPC chips adding instructions (Altivec, for example) to be more CISC like. There's also VLIW, which is much newer, and different from either CISC or RISC. The only VLIW chips I know of are Sun's MAJC, Intel's Itanium, and Transmeta's Crusoe.